Si半導体の研究業績紹介 Research Achievements in Si Semiconductors

MOSFET の微細化・性能向上のためには,ゲート長の縮小はもちろんソース・ドレインの浅接合形成技術の改善が不可欠となる.

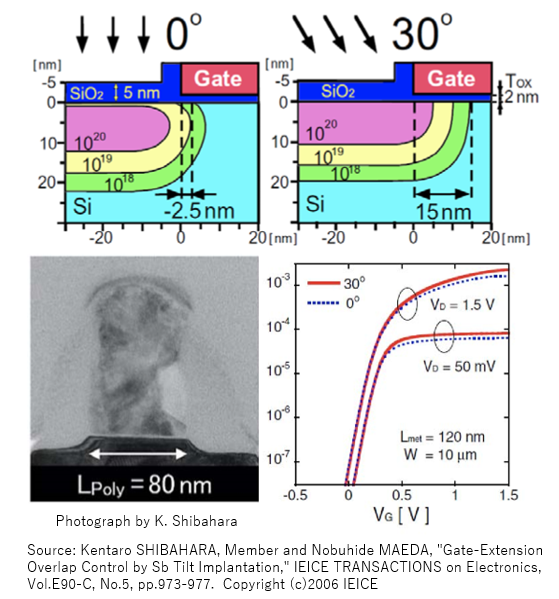

ゲート長 100 nm 以下,ゲート酸化膜 1.2 nm と極微細 MOSFET を実現(1998 年)した上,Sb イオン注入技術を開発した接合深さ 20 nm を達成し(1999 年),さらにソース・ドレインとゲートのオーバーラップ領域を充分に確保するための斜めイオン注入を提案し,電流駆動力の向上を実証した. (2002 年).

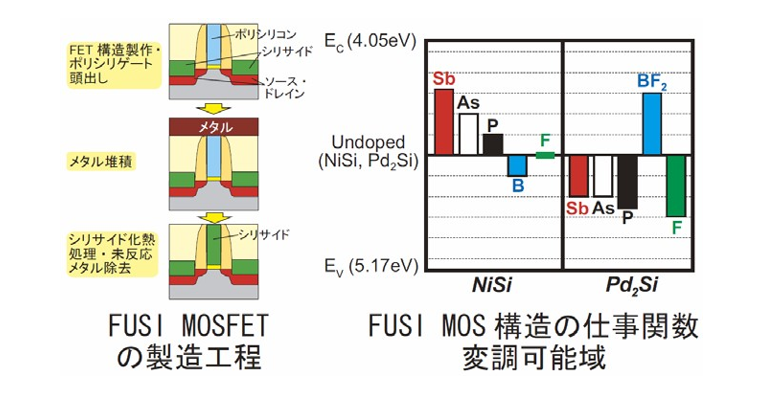

MOSFETのゲート電極をポリシリコンから空乏化の起こらない金属に置き換えると実効的ゲート絶縁膜薄層化が可能となるが,金属は仕事関数が材料固有であるために,同一金属でp型/n型MOSFETそれぞれに適したゲート仕事関数を得ることは不可能である.

そこで,Mo電極に固相拡散で窒素を導入する方法(2003 年)や,NiSi及びPd2Si フルシリサイドゲート(FUSI)のシリサイド化前のポリシリコンに不純物を添加することで,仕事関数の変調が可能であることを示した(2004~2006 年).

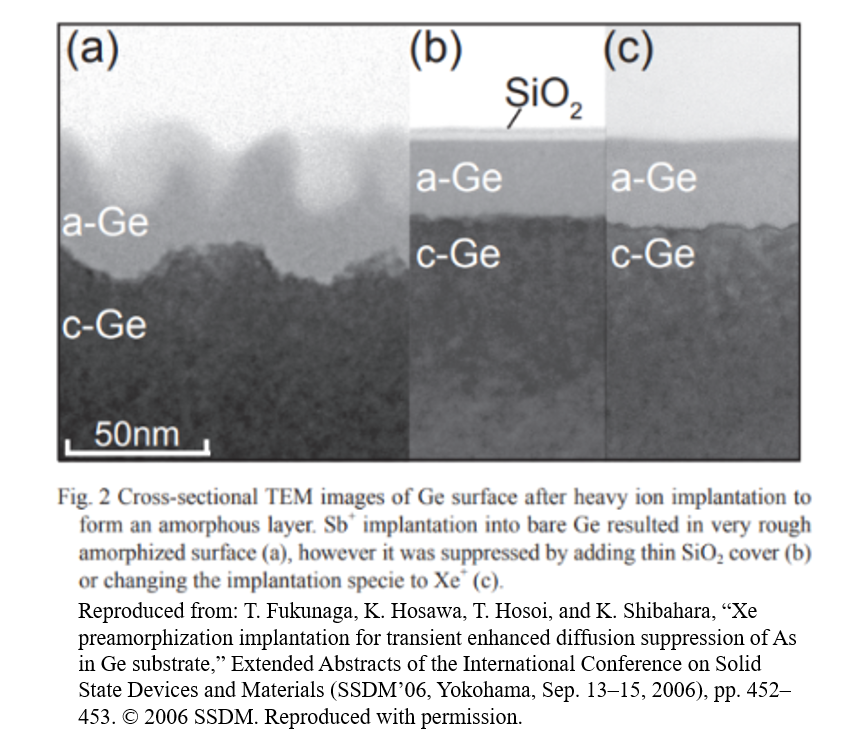

MOSFETの性能向上のために,Siに替わるチャネル材料としてGeが注目されているが,そのプロセス技術は未熟であり,ドーパント不純物の低い固溶度・高い拡散係数などが接合形成の課題である.

Geの場合,浅接合形成のために重イオン注入によるプレアモルファス化を行うと,Ge表面の揮発性酸化物の反応性脱離によって顕著な表面荒れが生じてしまうが((a) Sb注入),SiO2キャップ層((b))やXeイオンによるプレアモルファス化((c))によってそれが抑制できることを見出した(2006 年).